本文共 7515 字,大约阅读时间需要 25 分钟。

Catalogue

提取码:zb8b or 微信扫一扫:

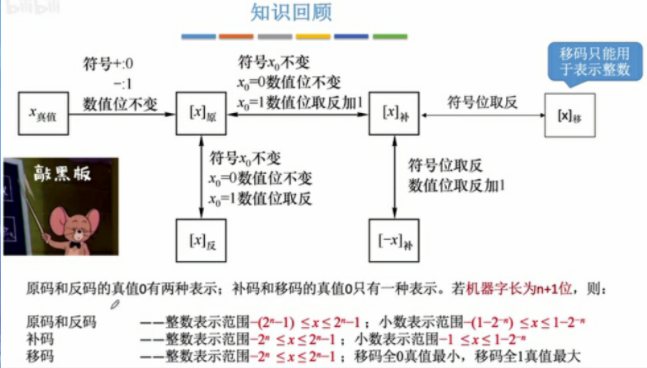

1.数据的编码表示(原、反、补、移码的编码和转换方法)

1.1知识储备

三种机器数的小结:

- 最高位为符号位,书写上用“,”/不写(整数)或“.”(小数)将数值部分和符号位隔开。

- 对于正数,原码=补码=反码

- 对于负数,符号位为1,其数值部分 原码除符号位外每位取反末位加1—>补码 原码除符号位外每位取反—>反码

1.2典型例题

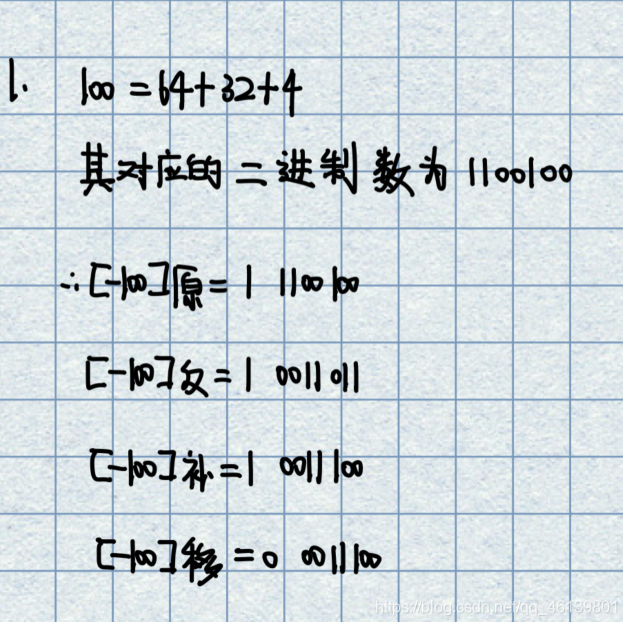

1、定点数x=-100,其8位原码是(1)、反码是(2)、补码是(3)、移码是(4)(例如10110110)参考解答: (1)1 1100100 (2)1 0011011 (3)1 0011100 (4)0 0011100

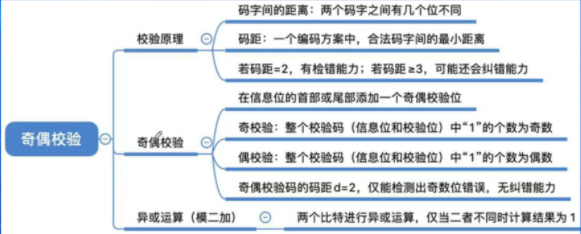

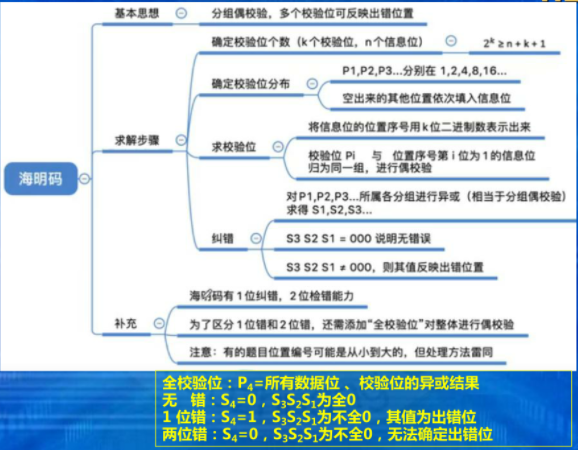

2.数据检错纠错方法(奇偶校验、海明编码解码与检错1、2和纠错1位方法并给出过程)

2.1知识储备

2.2典型例题

1.给出两个编码1001101和1010111的奇校验码和偶校验码。设最高位为校验位,余7位是信息位,则对应的奇偶校验码为:解析:奇校验码:整个校验码(有效信息位和校验位)中“1”的个数为奇数。偶校验码:整个校验码(有效信息位和校验位)中“1”的个数为偶数。参考解答:奇校验:11001101 01010111偶校验:01001101 11010111

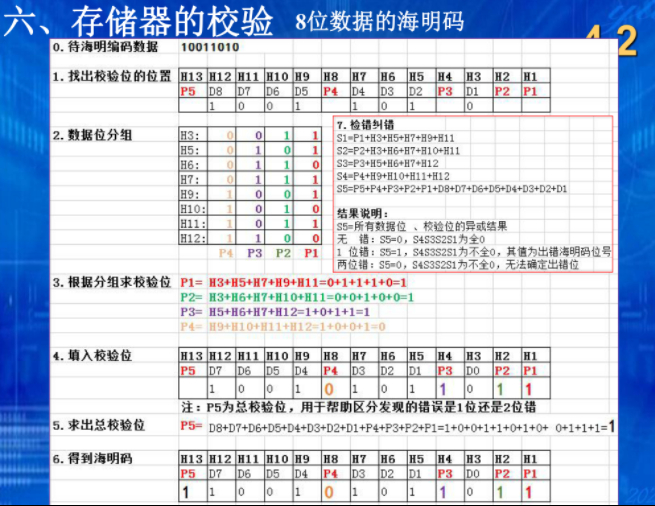

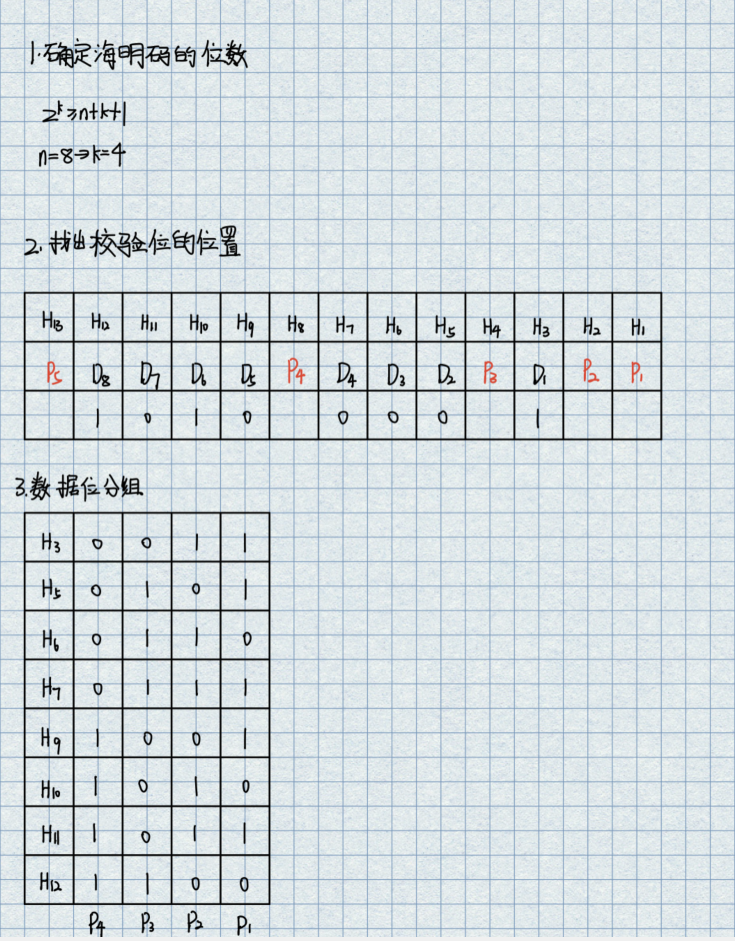

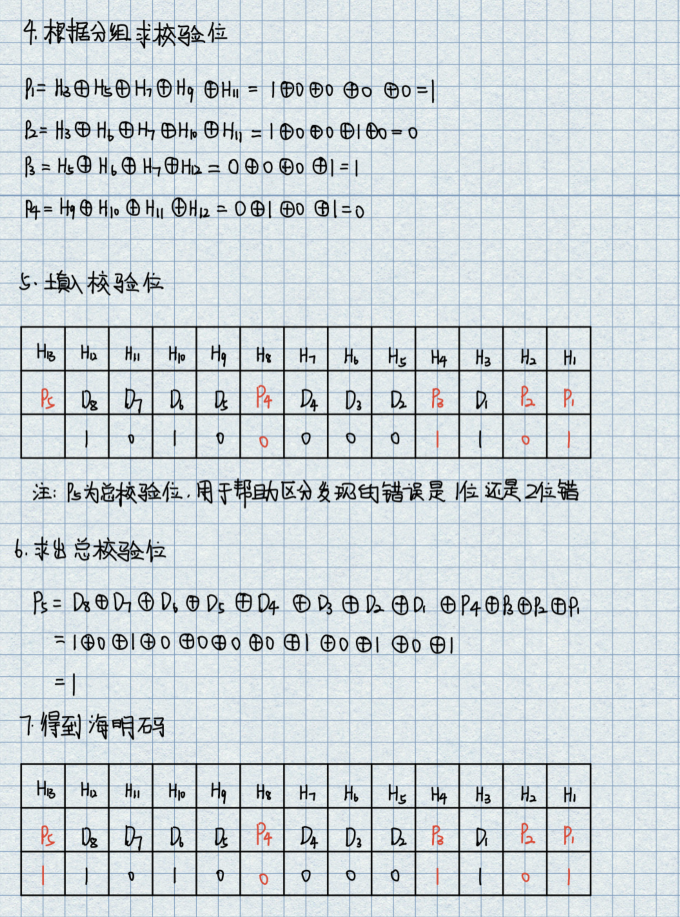

2.设待校验的数据为D8-D1=10100001,则采用海明校验,(1)求其海明码(设海明码具有一位纠错能力,H13采用全校验)。给出海明码求解过程。(2)假设信息传输前10100001–>传输后10101001,给出海明码检错纠错过程。参考解答:(1)

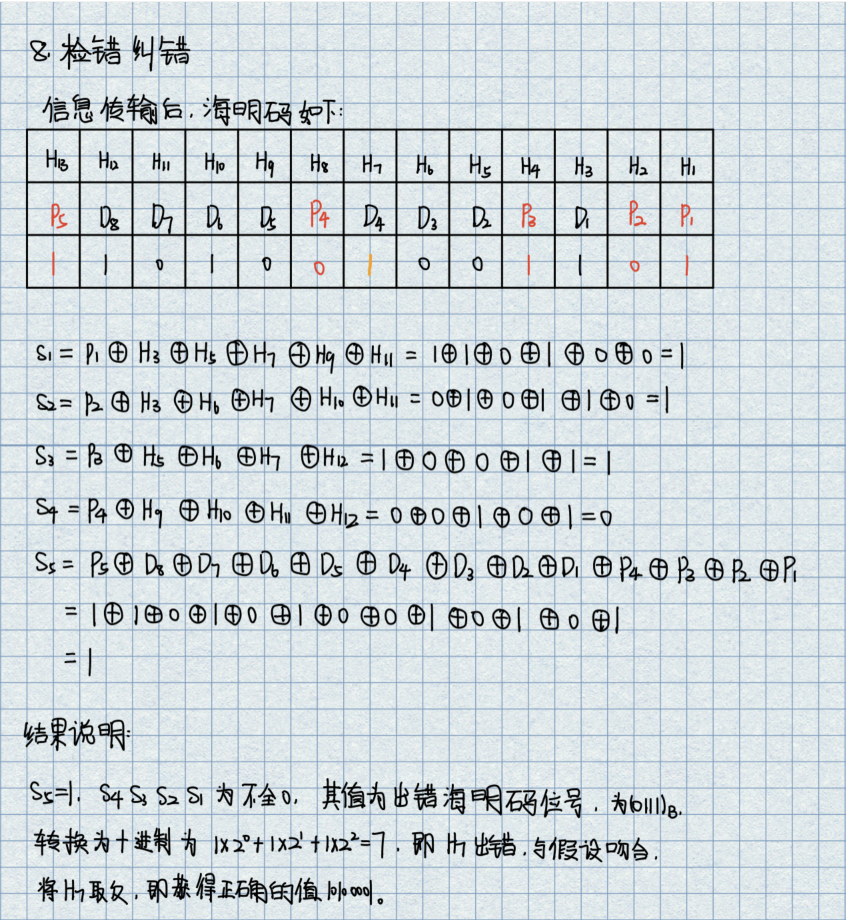

(2)

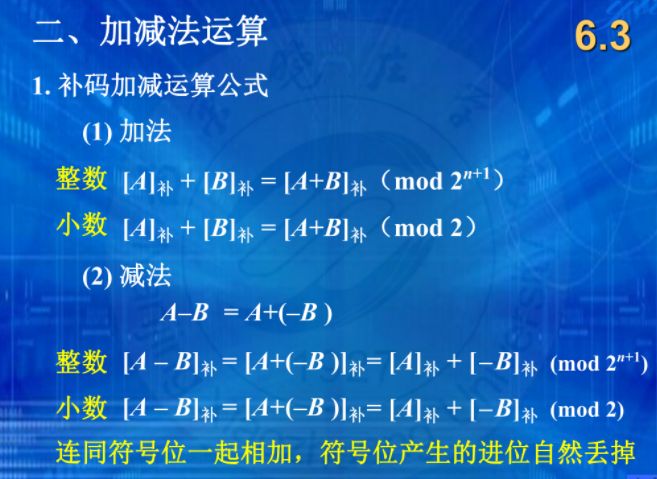

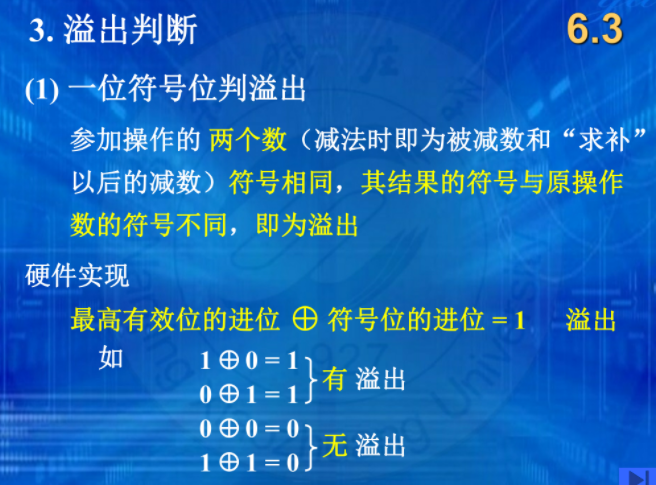

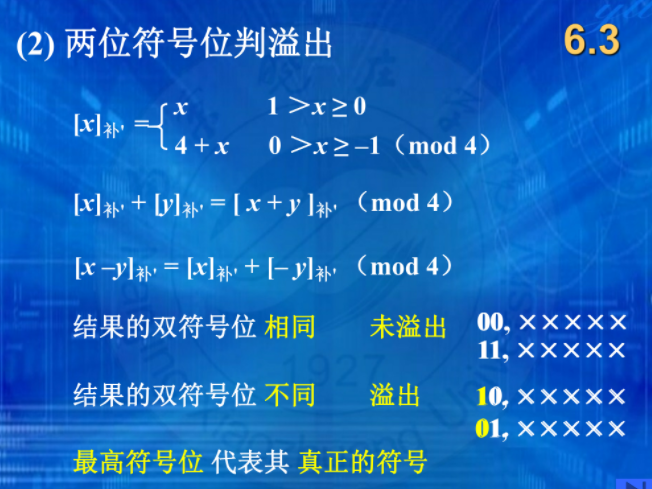

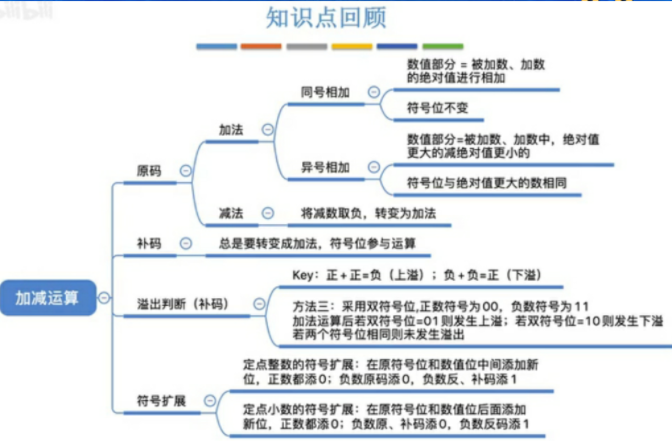

3.定点数补码加减法及溢出判断

3.1知识储备

3.2典型例题

9、若机器字长为8位,用定点小数表示。已知X=-0.10110,Y=0.10010。求[X]补=(1)[Y]补=(2)和[-Y]补=(3)(格式如1.0101010)用变形补码计算[X+Y]补=(4)(格式如:11.0101010)。并判断结果(5)(有或无)溢出。用变形补码计算[X-Y]补= (6)(格式如:11.0101010)。并判断结果(7)(有或无)溢出。参考解答:(1)1.0101000 (2)0.1001000 (3)1.0111000(4)11.1110000 (5)无 (6)10.1100000 (7)有

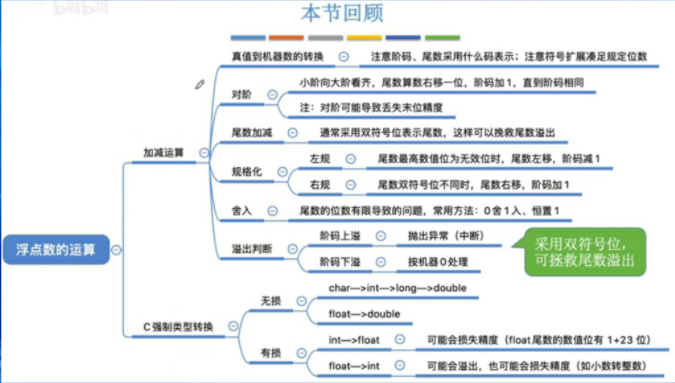

4.浮点数加减法

4.1知识储备

-

左规,是为了去掉真值小数点后的零,符号位不能动,所以是算术左移。

-

右规,是为了把进位到符号位的值移到小数点后面来,采用双符号位,

既可以保留原符号位,又可以保留进位位,所以这个地方的右移是需要保留符号位的,是算术右移。 -

规格化浮点数:规定尾数的最高数值位必须是一个有效值。

-

原码表示的尾数规格化:尾数的最高数值位必须是1。

-

补码表示的尾数规格化:尾数的最高数值位必须和尾数的符号位相反。

4.2典型例题

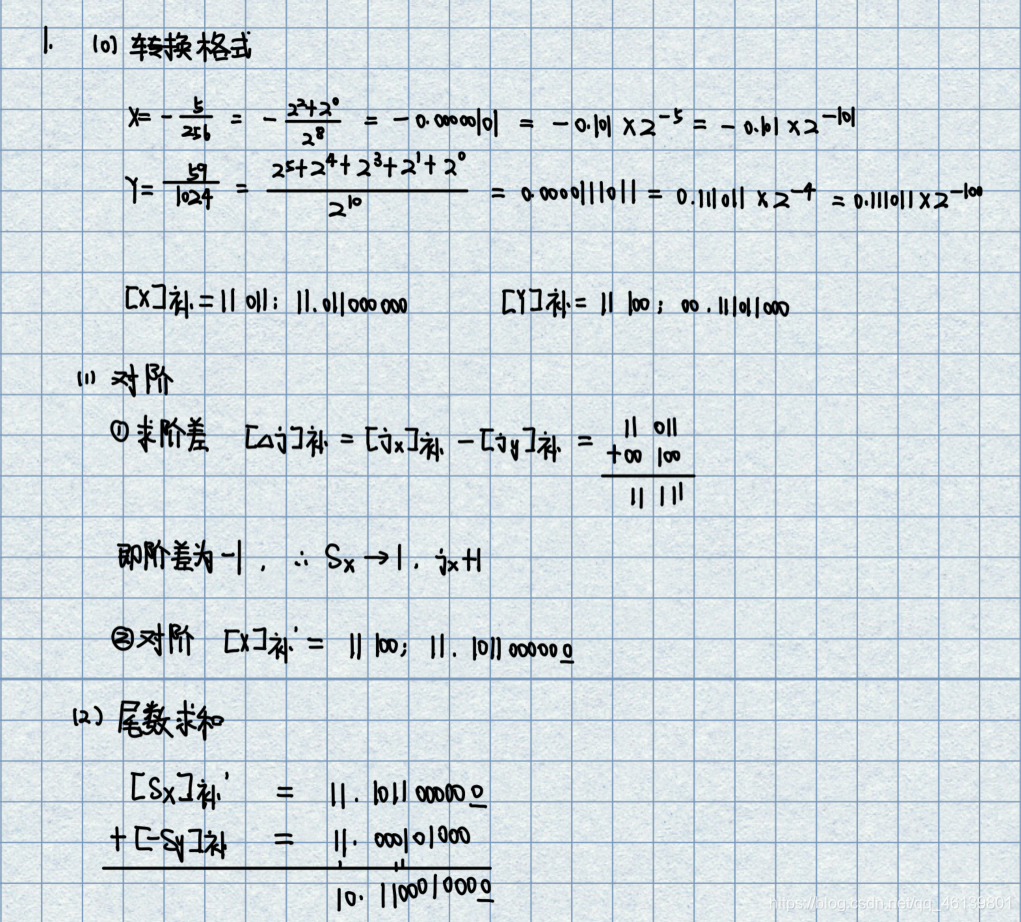

1.已知十进制数X=-5/256,Y=+59/1024,舍入用0舍1入法,按机器补码浮点运算规则计算X-Y,结果用二进制表示。浮点数格式如下:阶符取2位,阶码取3位,数符取2位,尾数取9位。参考解答:

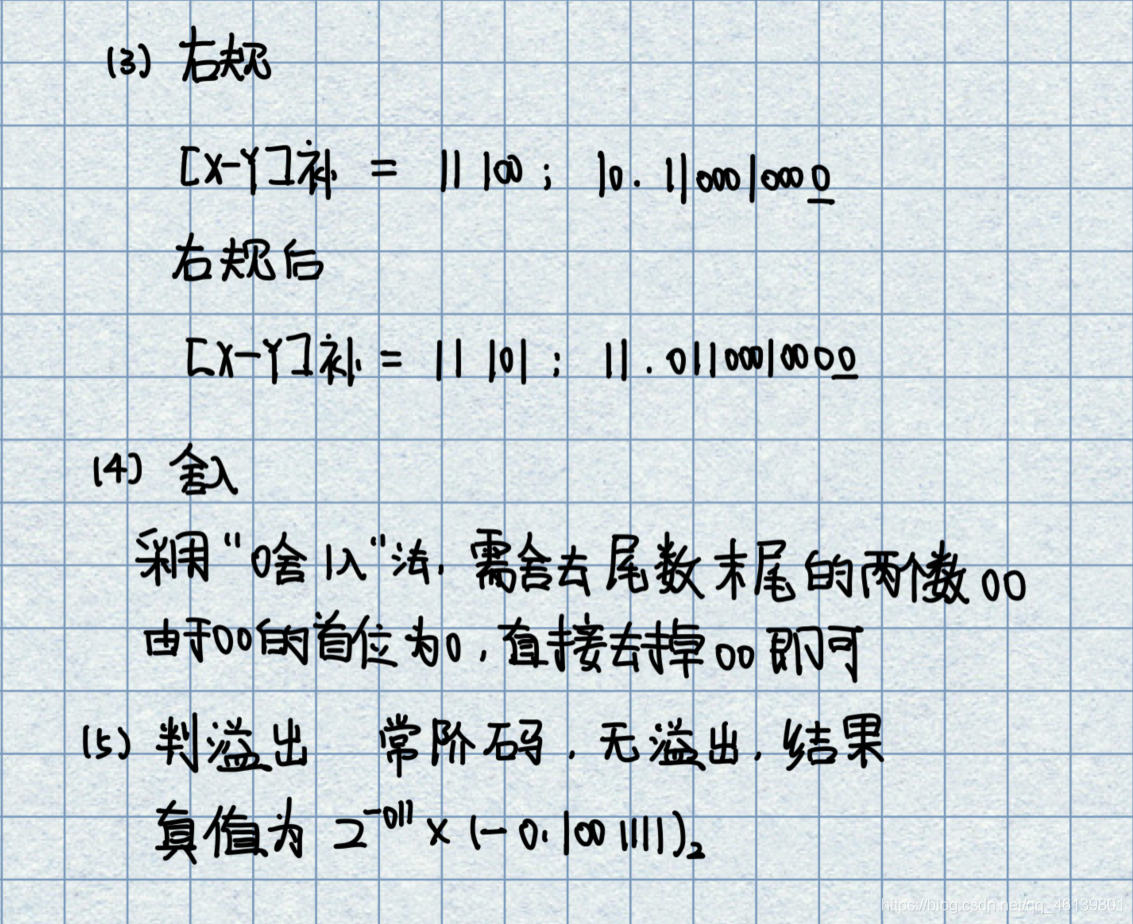

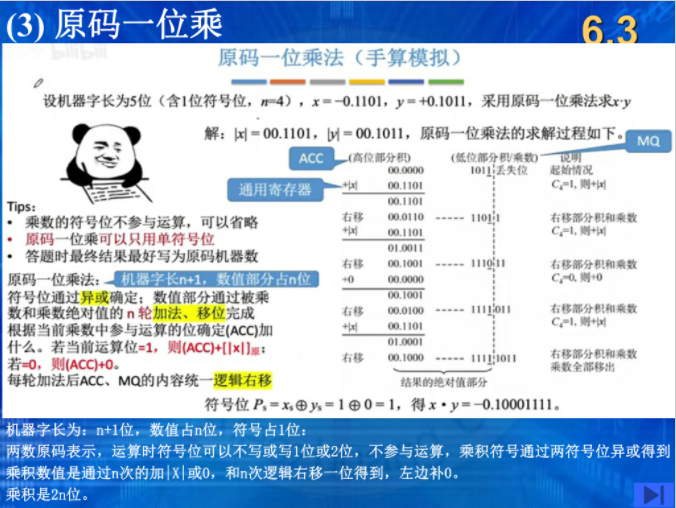

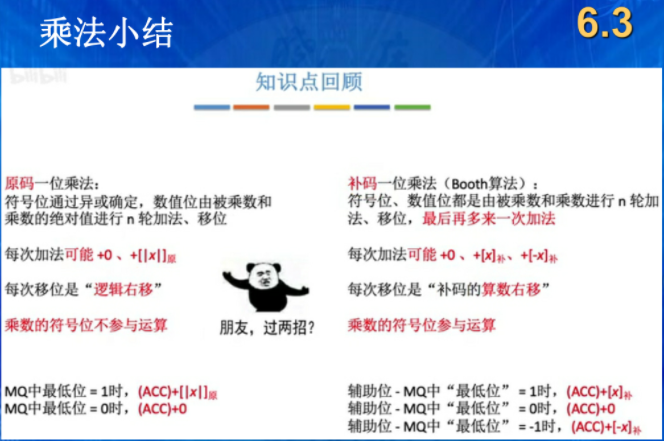

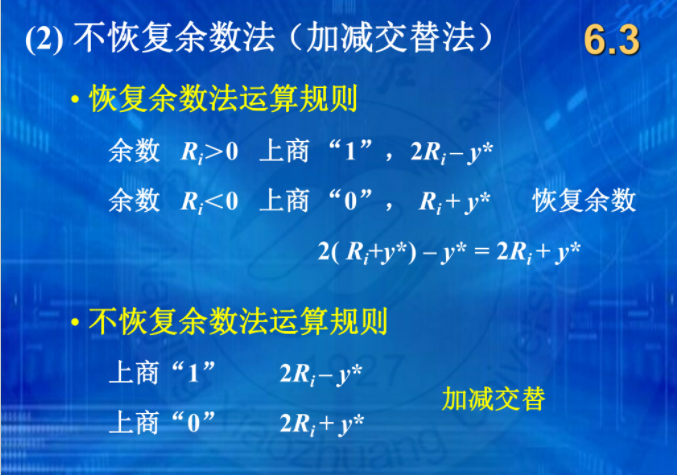

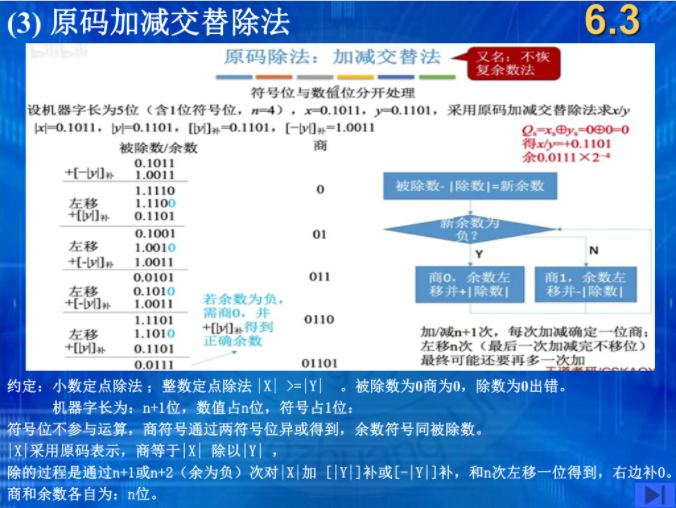

5.定点数乘除法(原码/布斯法补码一位乘法,加减交替法原码一位除)

5.1知识储备

5.2典型例题

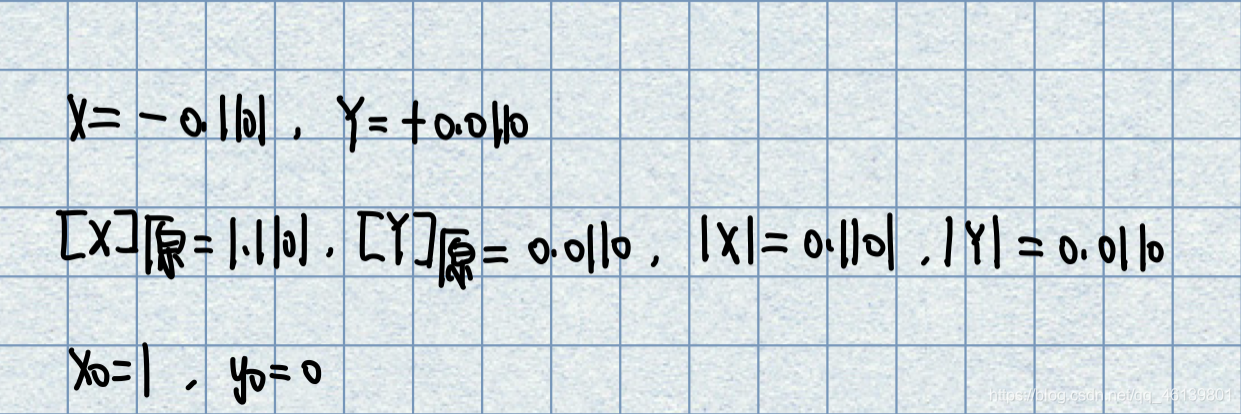

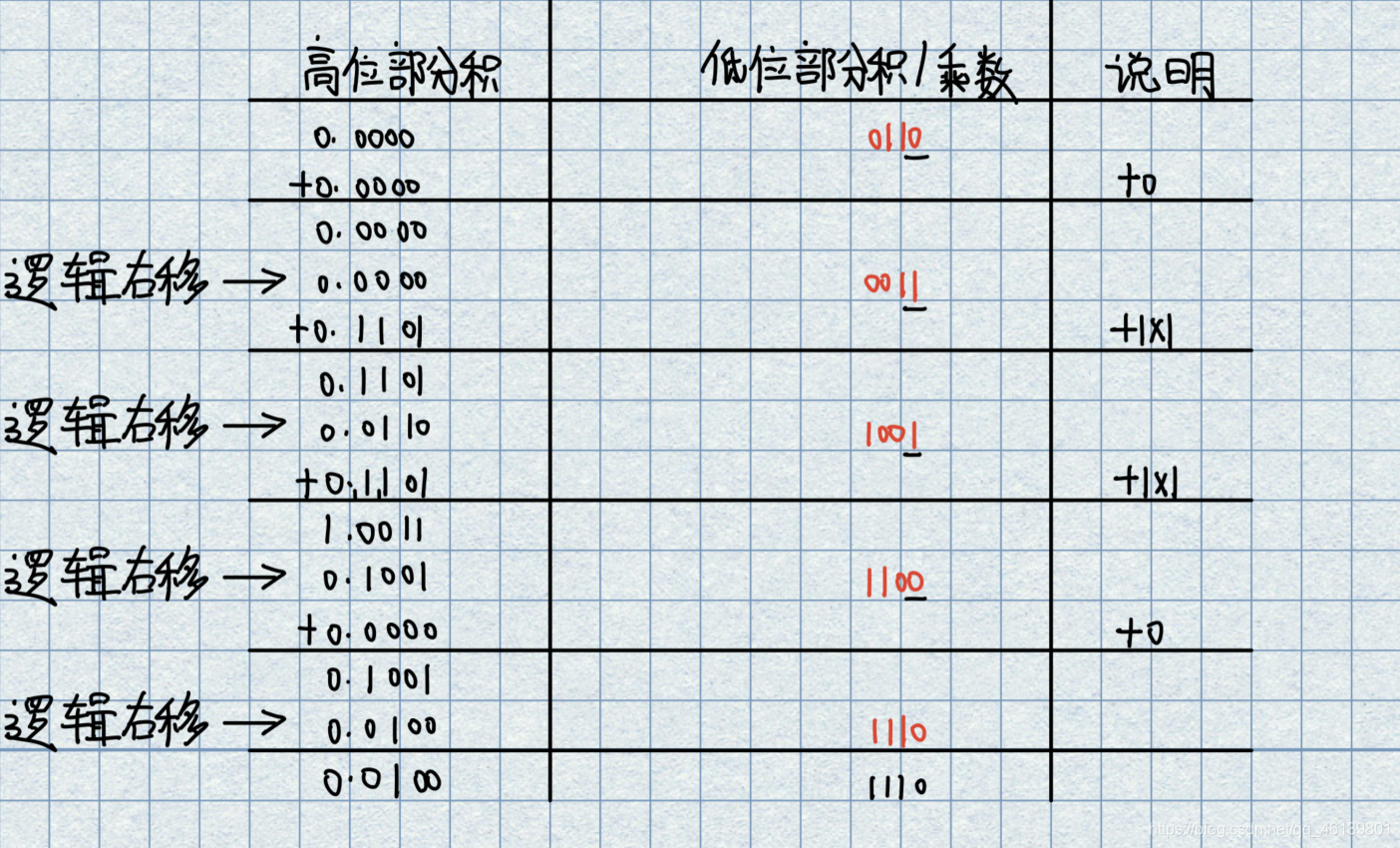

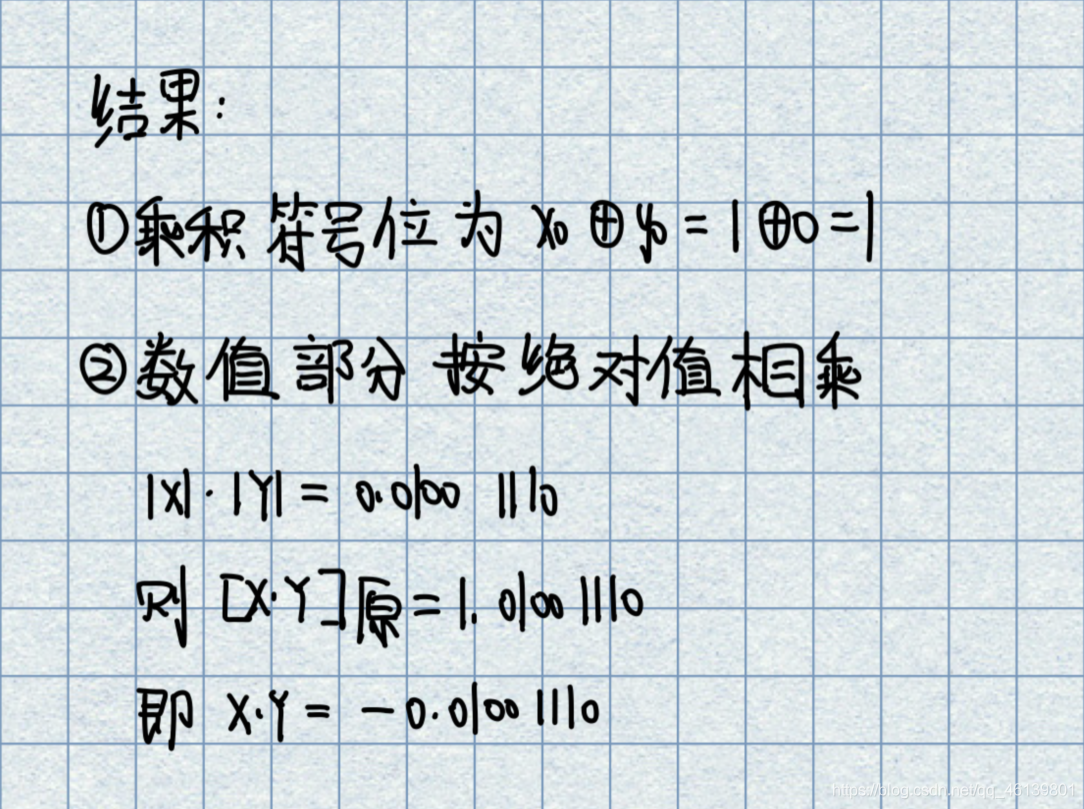

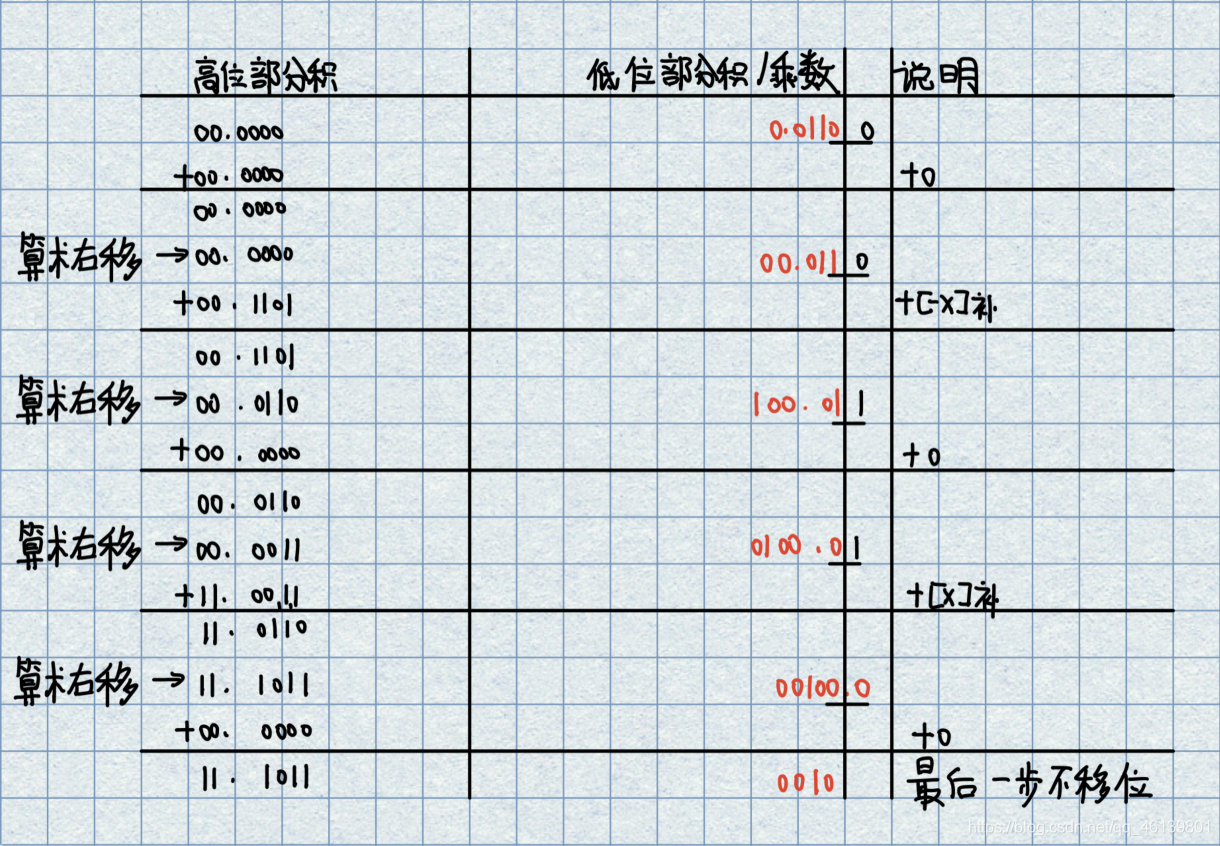

1.根据题中数据用原码一位乘法求乘积,并写出计算步骤,设机器字长为5位二进制。X= -0.1101,Y=+0.0110参考解答:

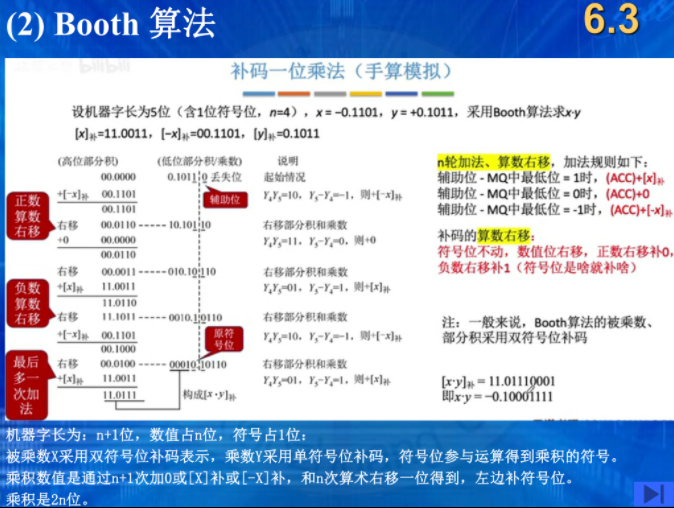

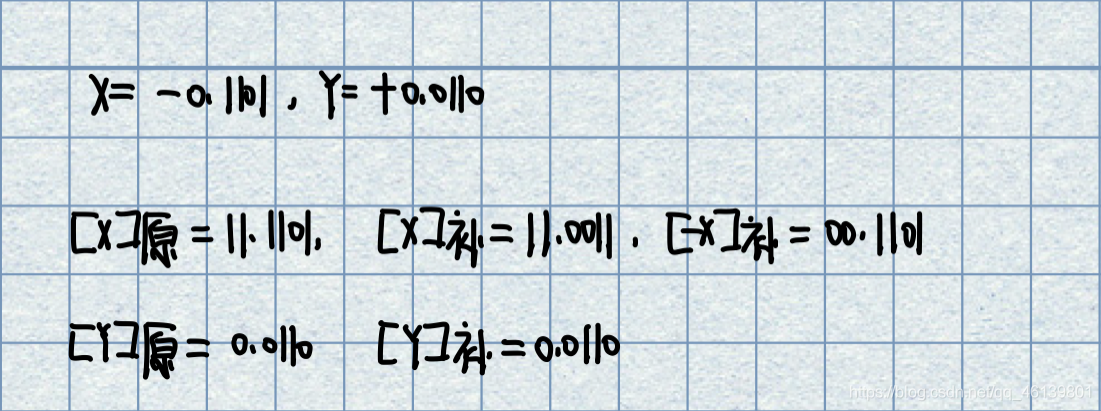

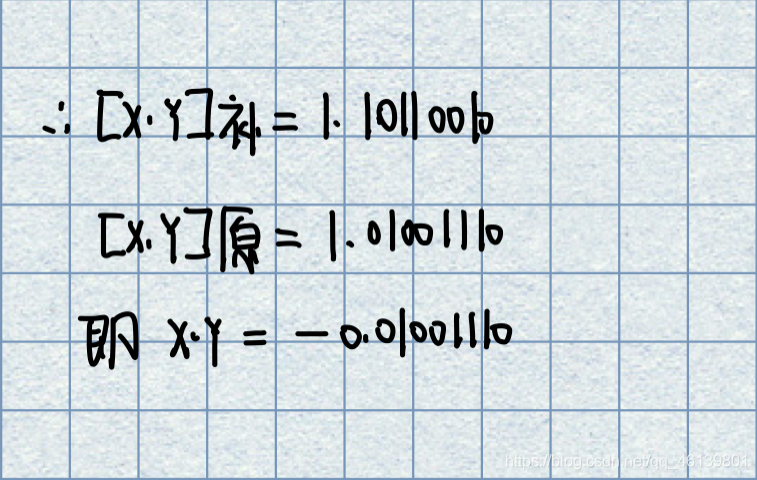

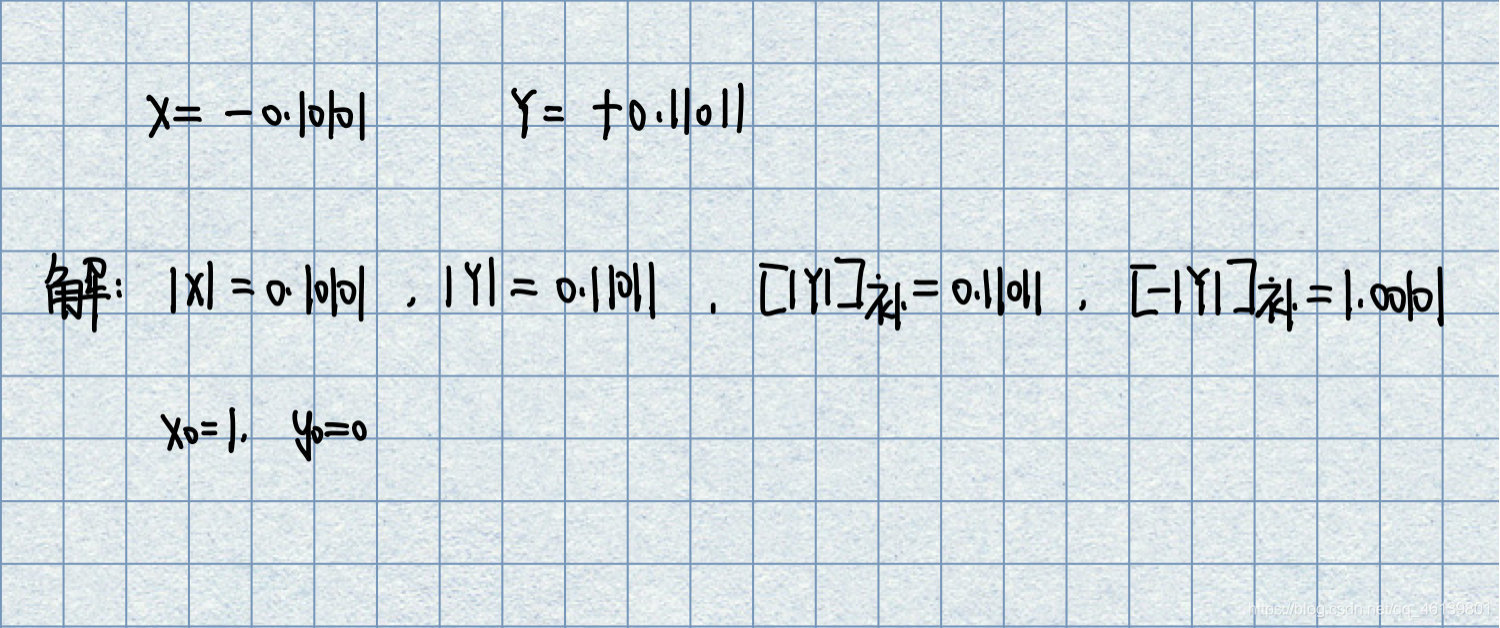

2.根据题中数据用补码一位乘法(布斯法)求乘积,并写出计算步骤,设机器字长为5位二进制。X= - 0.1101,Y=+0.0110参考解答:

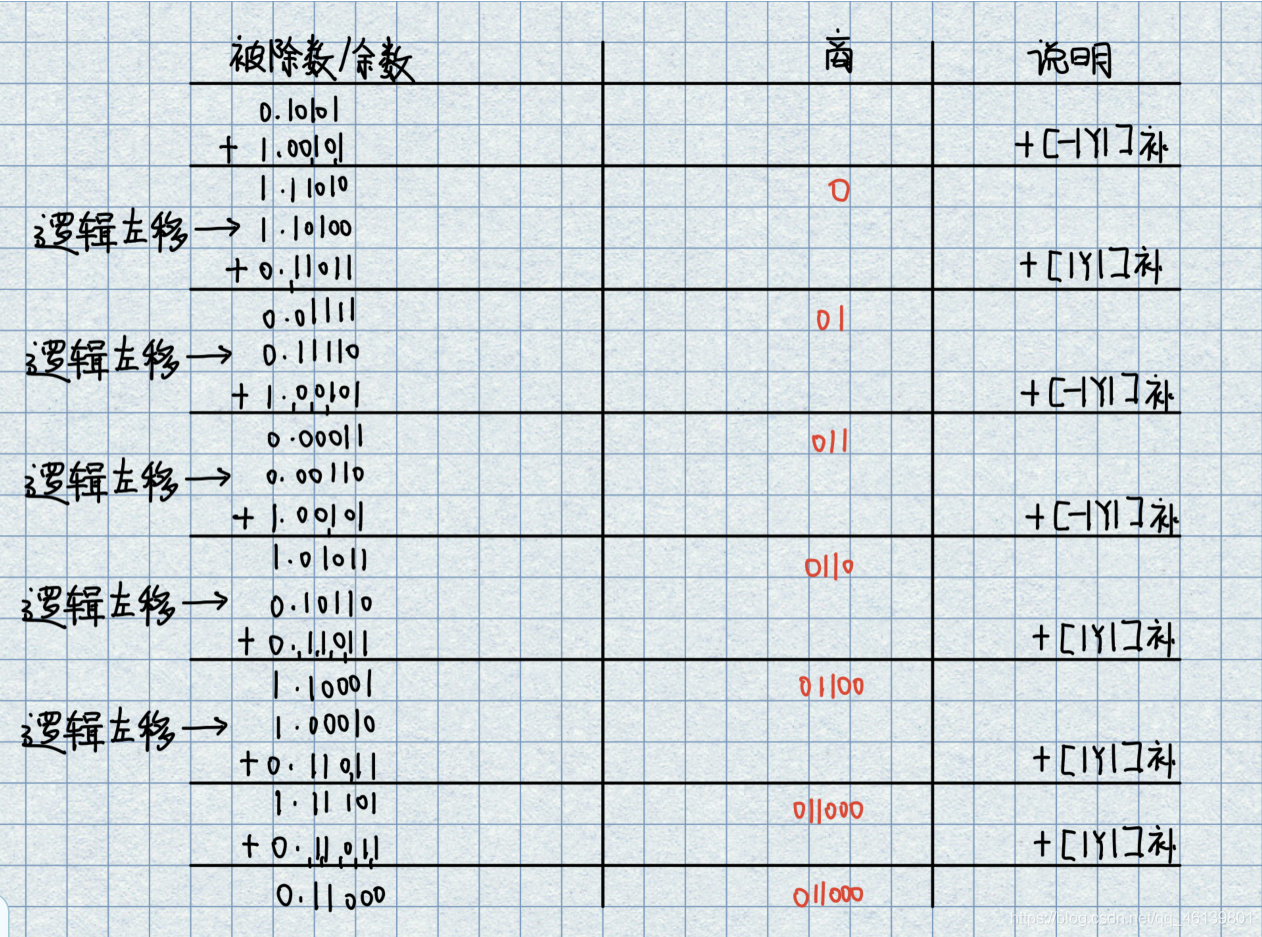

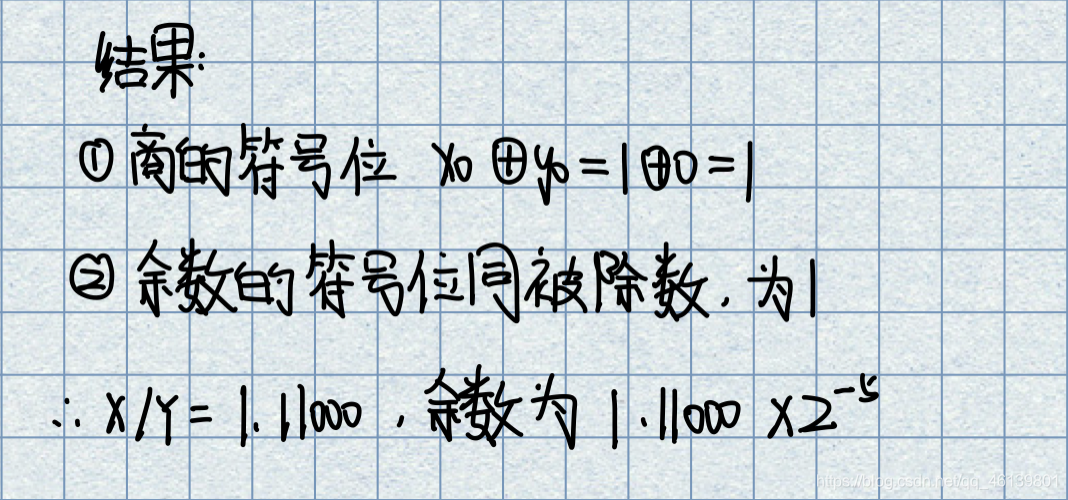

3.请用原码加减交替法完成 X除以 Y的运算,并写出运算步骤,设机器字长为6位二进制。X=-0.10101,Y=+0.11011参考解答:

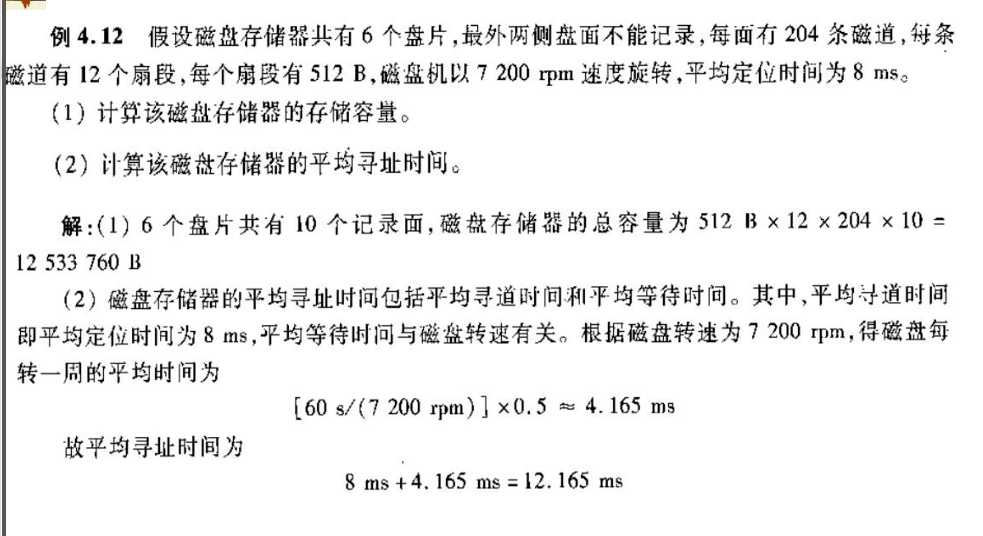

6.磁盘计算(容量、平均等待时间、平均寻址时间、最大数据传输率等计算)

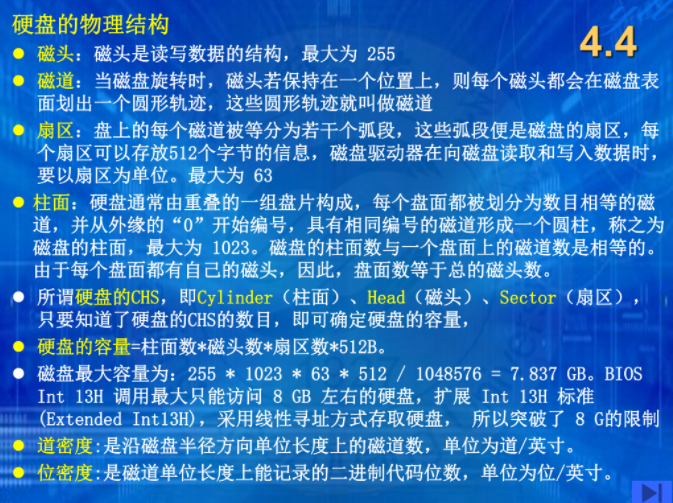

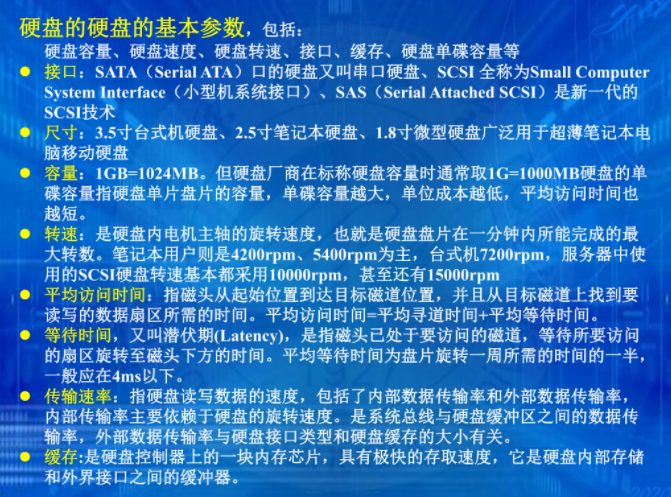

6.1知识储备(书本P124、125)

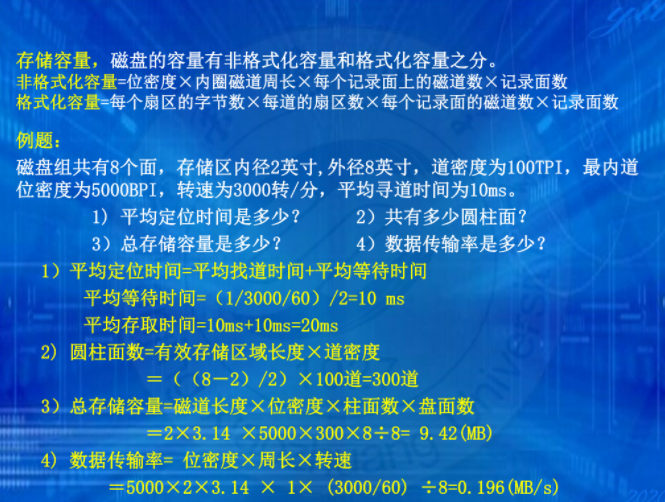

- 磁盘存储器的存储总容量C=n X k X s,其中n为存放信息的盘面数,k为每个盘面的磁道数,s为每条磁道上记录的二进制代码数。

- 磁盘平均等待时间,又叫潜伏期,是指磁头已处于要访问的磁道,等待所要访问的扇区旋转至磁头下方的时间。平均等待时间为盘片旋转一周所需的时间的一半。

- 平均寻址时间=平均找道时间+平均等待时间。

- 数据传输率=位密度 X 线速度,又线速度=周长 X 转速 ,因此数据传输率=位密度 X 周长 X 转速。又位密度 X 周长=每个磁道的总位数,因此数据传输率=每个磁道的总位数 X 转速。

6.2典型例题

2.每条磁道有12个扇段,每个扇段有512B,磁盘机以7200rpm速度旋转。求磁盘数据传输率。参考解答:

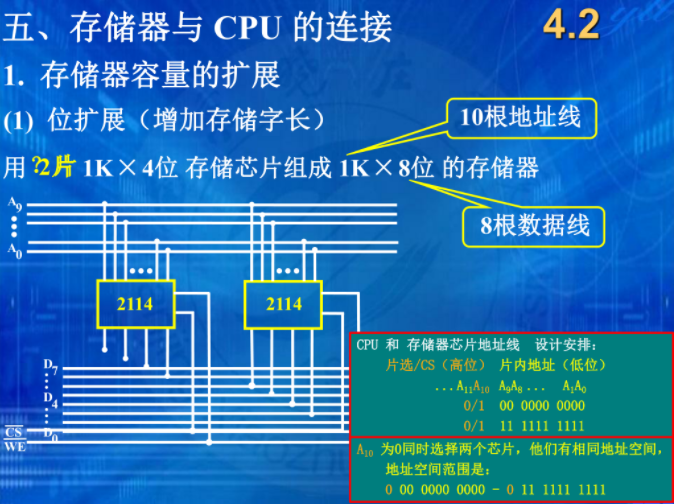

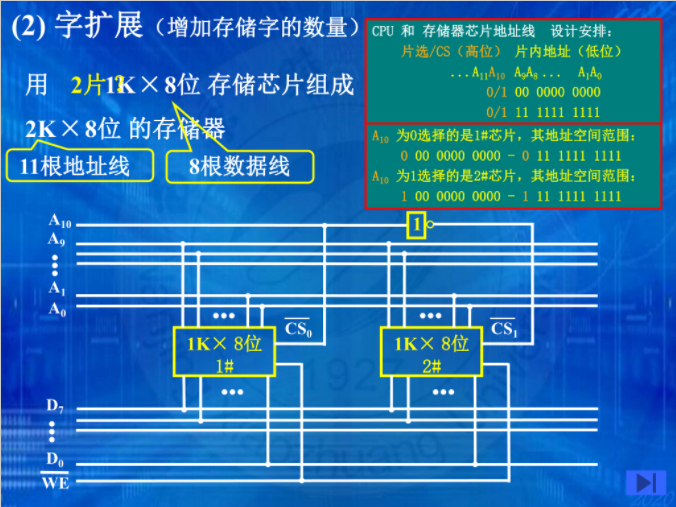

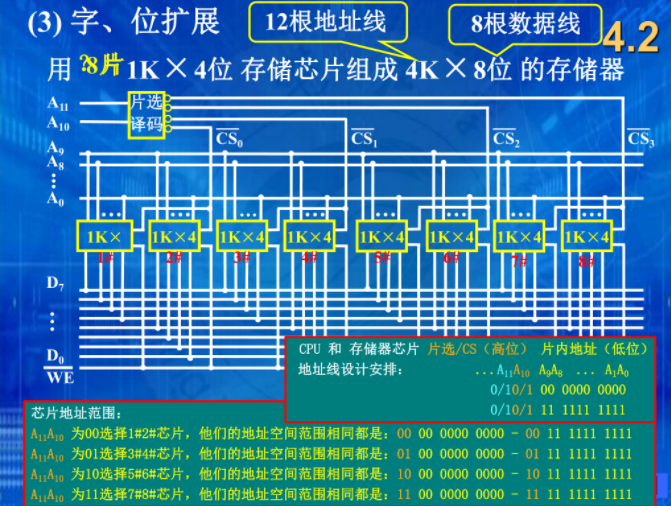

7.存储器系统(根据条件选择若干芯片、连接线路、给出扩展连接图和地址空间简单分析)

7.1知识储备

注:位扩展扩展的是数据位宽度,字扩展扩展的是CPU访问存储空间的容量。

7.2典型例题

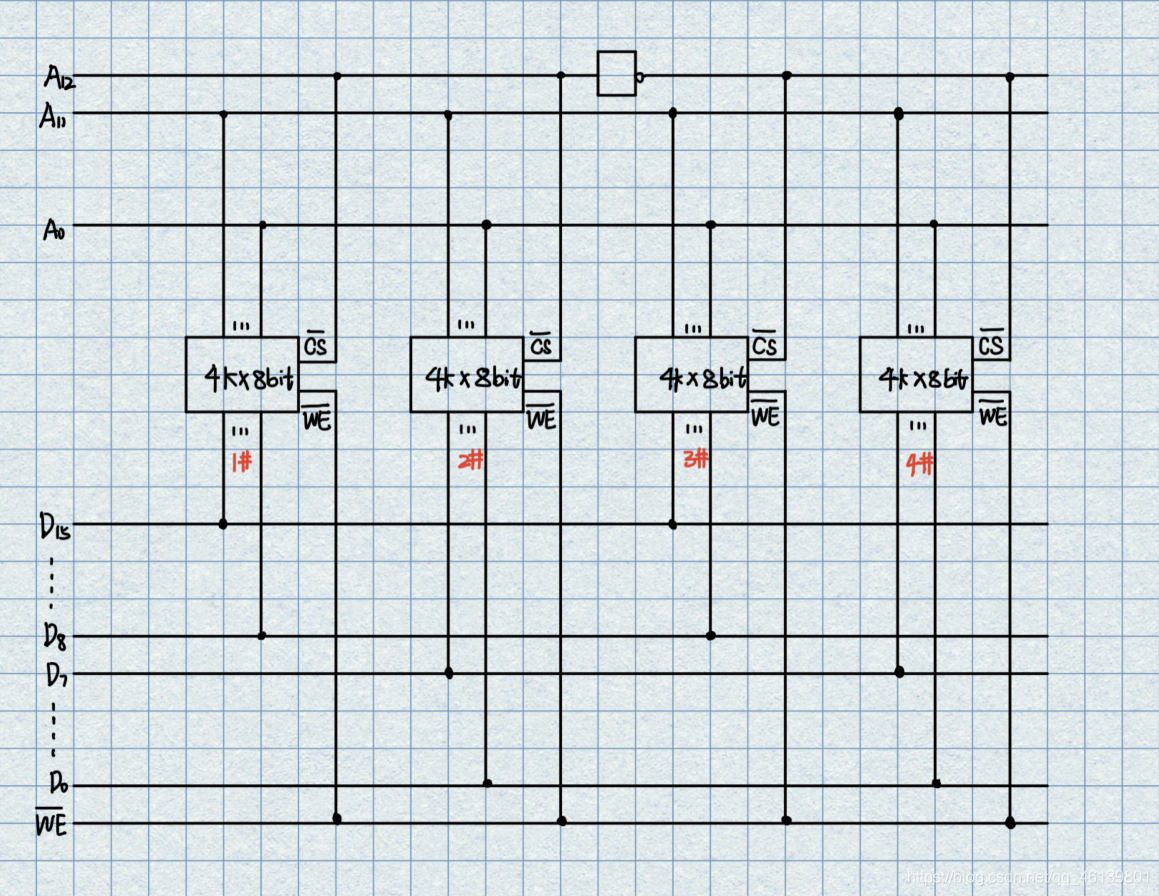

1、使用4K x 8位的RAM芯片组成一个容量为8K x 16位的存储器,需要(1)片,进行(2)扩展,需要连接(3)根地址线,(4)根数据线,还需要连接一根(5),一根(6)。画出连线图,给出其存储器地址范围。参考解答:(1)4(2)字、位(3)13(4)16(5)片选线(6)读写控制线

A12为0时,选择的是1#、2#芯片,它们的地址空间范围相同,都是0 000000000000~0 111111111111。A12为1时,选择的是3#、4#芯片,它们的地址空间范围相同,都是1 000000000000~1 111111111111。

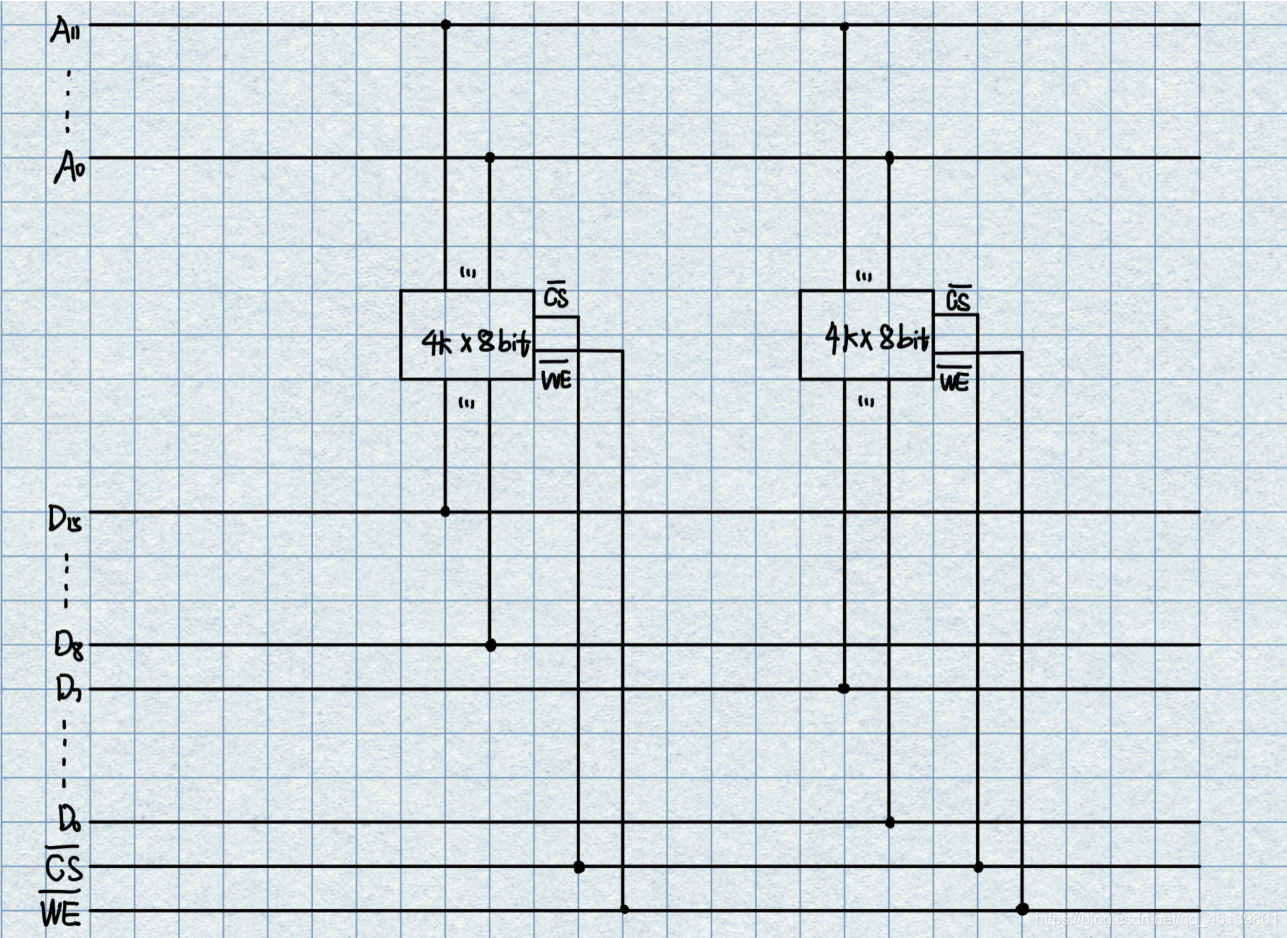

2、使用4K x 8位的RAM芯片组成一个容量为4K x 16位的存储器,需要(1)片,进行(2)扩展,需要连接(3)根地址线,(4)根数据线,还需要连接1根(5),一根(6)。画出连线图,给出其存储器地址范围。参考解答:(1)2(2)位(3)12(4)16(5)片选线(6)读写控制线

CS非为0时,同时选择两个芯片,它们有相同地址空间,地址空间范围是:0 000000000000~0 111111111111

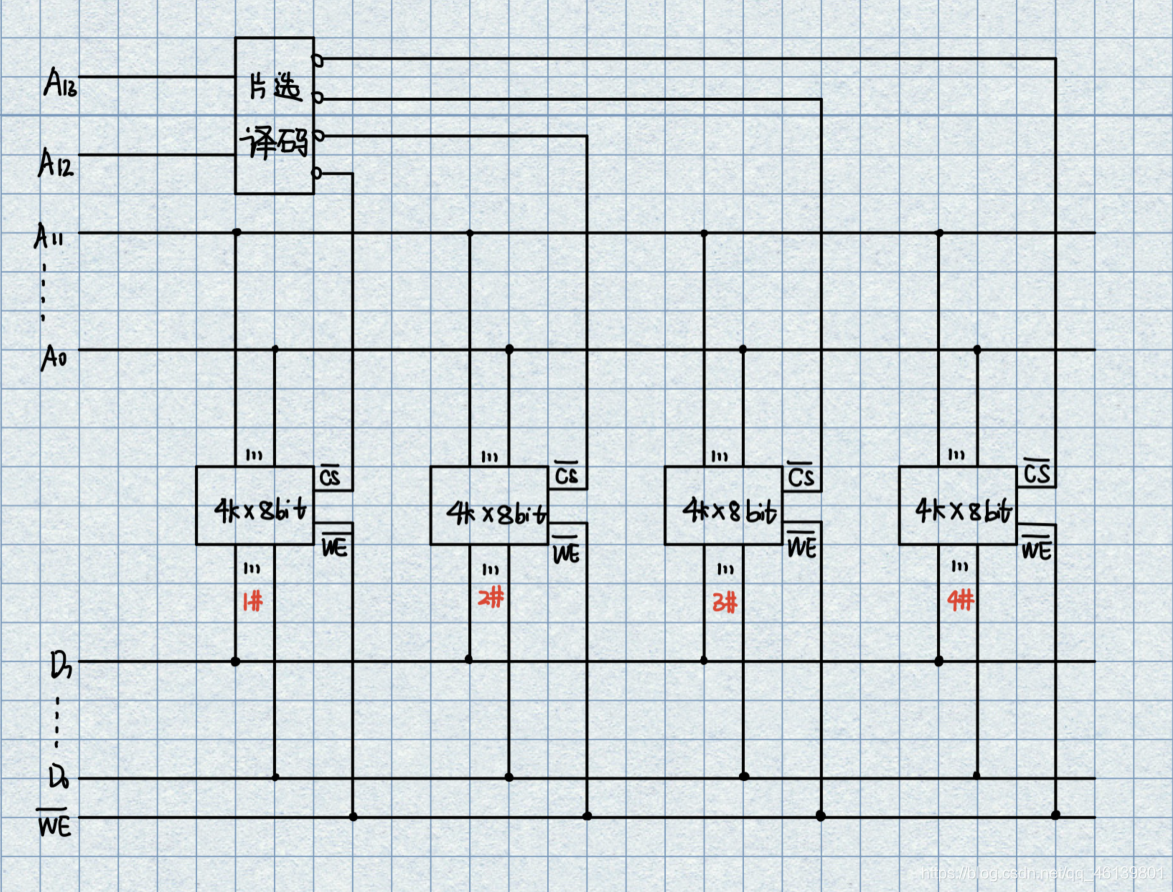

3、使用4K x 8位的RAM芯片组成一个容量为16K x 8位的存储器,需要(1)片,进行(2)扩展,需要连接(3)根地址线,(4)根数据线,还需要连接1根(5),一根(6)。画出连线图,给出其存储器地址范围。参考解答:(1)4(2)字(3)14(4)8(5)片选线(6)读写控制线

A13A12为00时,选择的是1#芯片,其地址空间范围为00 000000000000~00 111111111111A13A12为01时,选择的是2#芯片,其地址空间范围为01 000000000000~01 111111111111A13A12为10时,选择的是3#芯片,其地址空间范围为10 000000000000~10 111111111111A13A12为11时,选择的是4#芯片,其地址空间范围为11 000000000000~11 111111111111

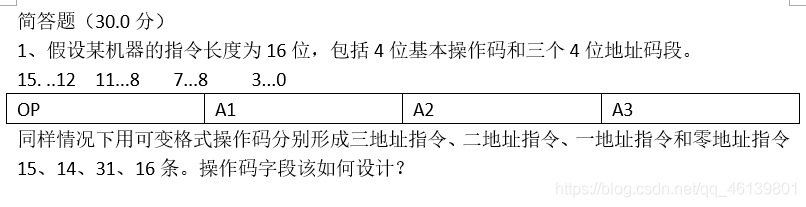

8.指令系统(定长操作码数量计算、不定长操作码的数量计算和根据条件的编码扩展)

8.1知识储备

8.2典型例题

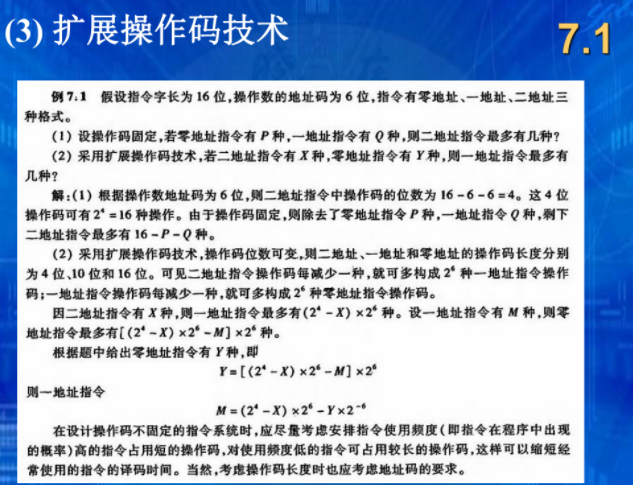

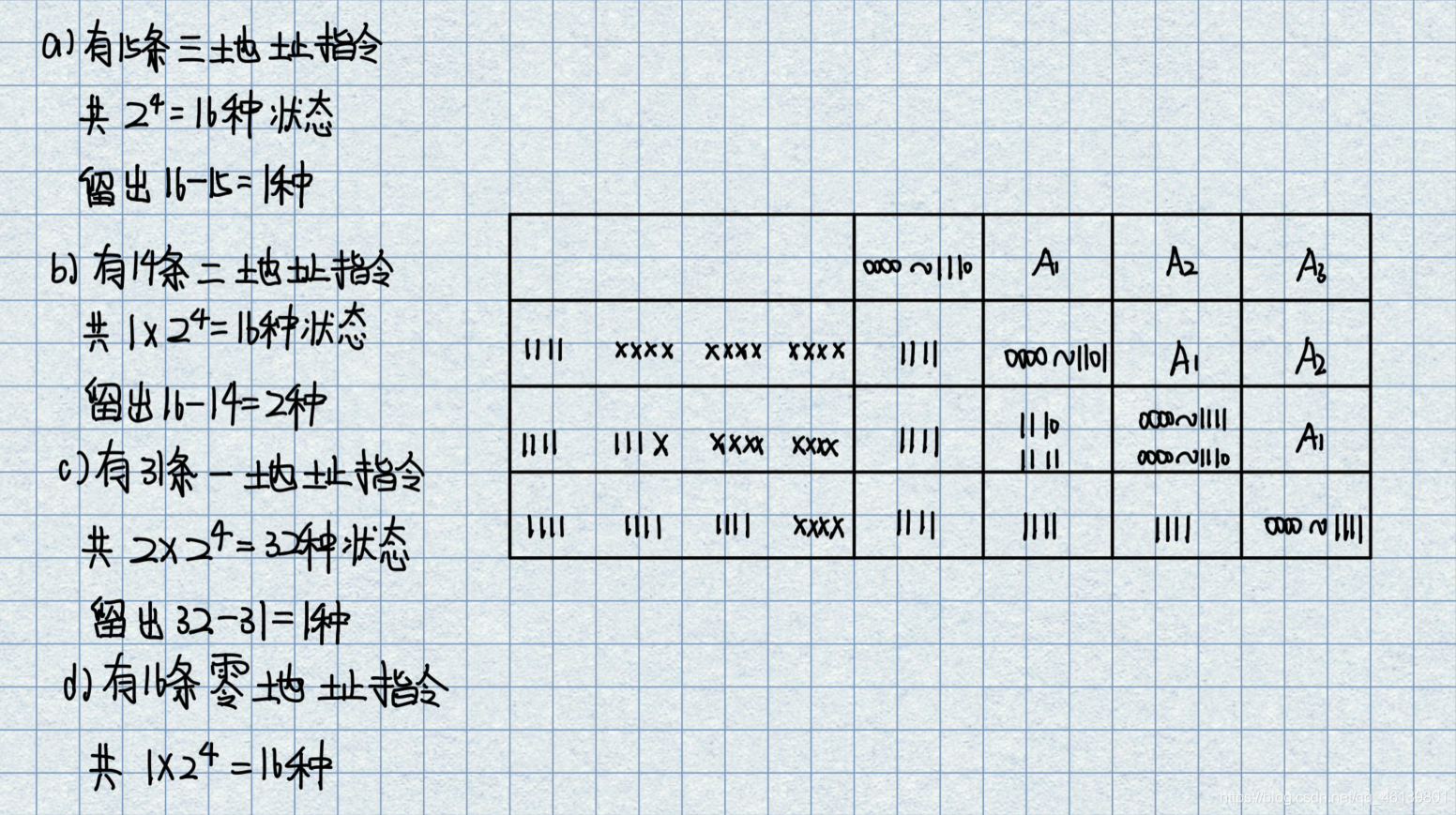

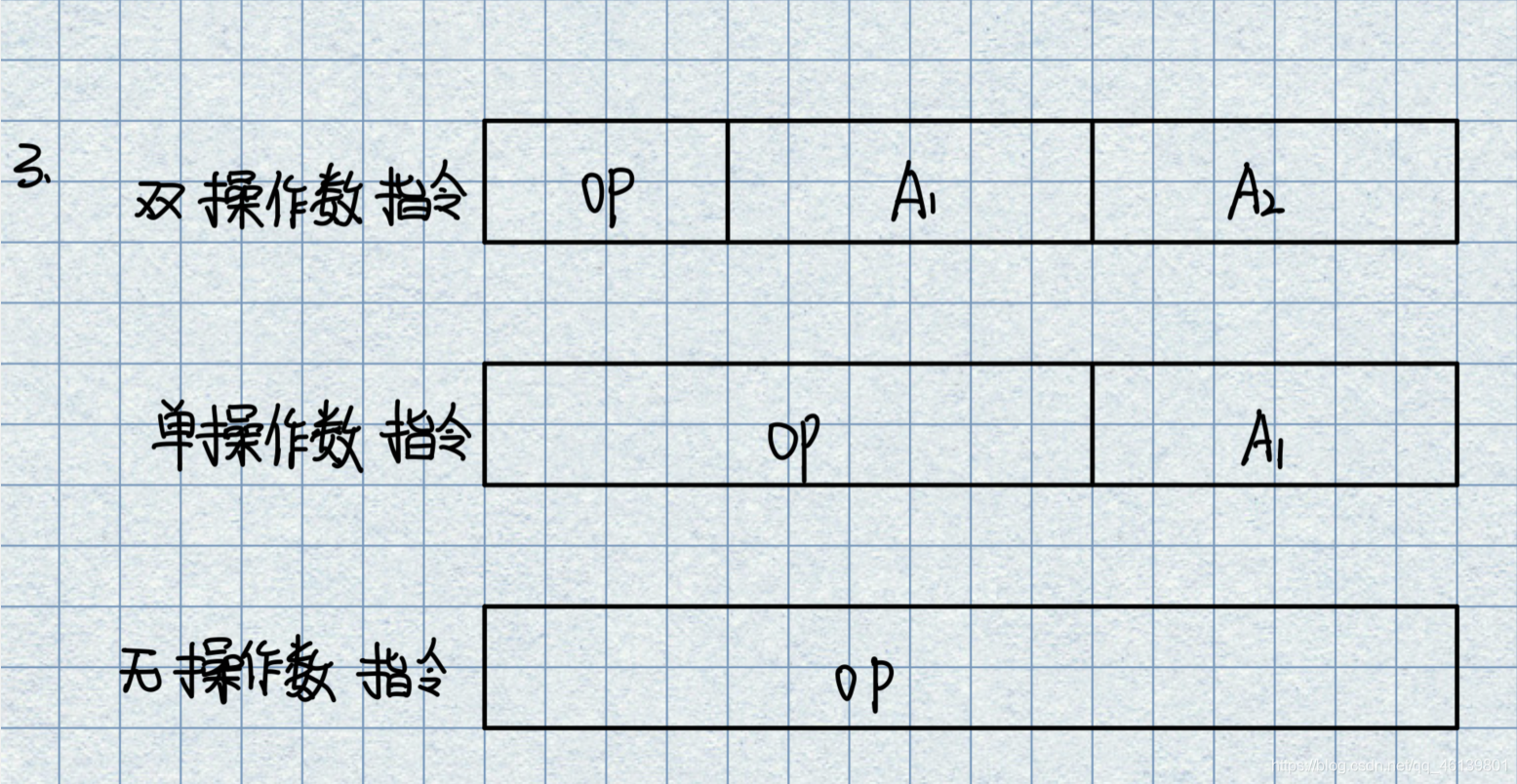

1.假设某计算机的指令长度固定为16位,具有双操作数,单操作数和无操作数三类指令, 每个操作数地址规定用6位表示。 (1)现已设计出m条双操作数指令,n条无操作数指令, 在此情况下,这台计算机最多可设计出多少条单操作数指令? (2)当双操作数指令取最大数,且在此基础上,单操作数指令条数也取最大值, 试计算这3类指令最多可拥有多少条指令? 参考解答:

(1)计算机最多有2^4=16条双操作数指令,双操作数指令为m条,则操作码字段还有16-m种扩展标志,用于表示操作码向一地址字段扩展,计算机最多有(16-m)X 2^6条单操作数指令;又无操作数指令是在单操作数指令的基础上,通过将操作码向最后一个地址字段扩展得到的,加上扩展的过程中用了y个扩展标志,则有无操作数指令n=y X 2^6=64y,y=n/64;因此计算机最多可设计出(16-m) X 64-n/64条单操作数指令。(2)双操作数指令最多有2^4-1=15条单操作数指令最多有1*2^6-1=63条无操作数指令最多有1*2^6=64条

2.假设某计算机指令长度为20位,具有双操作数、单操作数和无操作数3类指令格式,每个操作数地址规定用6位表示。问:若操作码字段固定为8位,现已设计出m条双操作数指令,n条无操作数指令,在此情况下,这台计算机最多可以设计出多少条单操作数指令?参考解答:由于设定全部指令采用8位固定的OP字段,故这台计算机最多的指令条数为2^8=256条。因此最多还可以设计出(256-m-n)条单操作数指令。

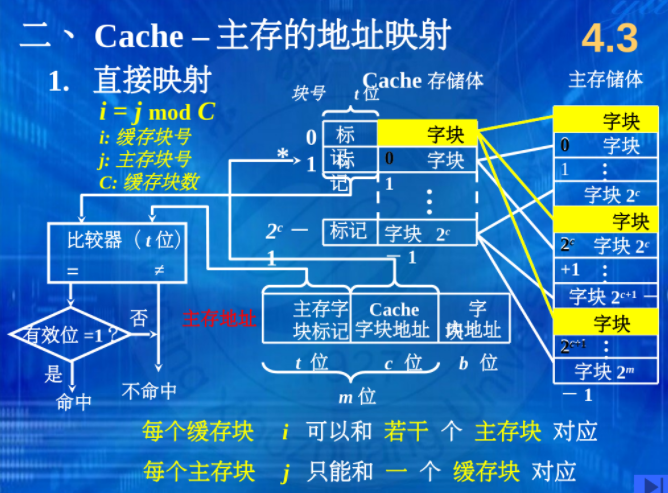

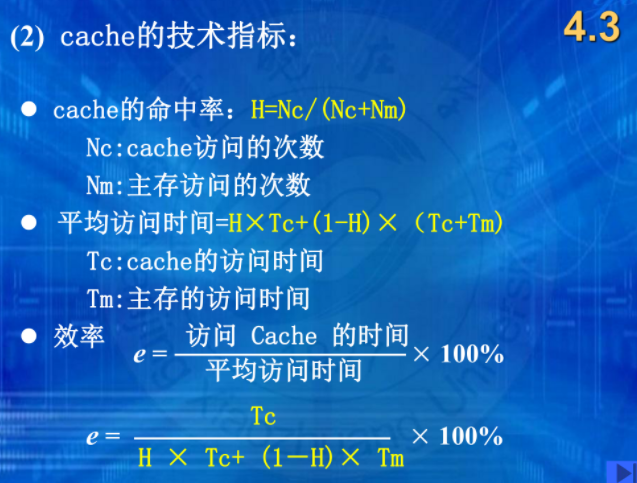

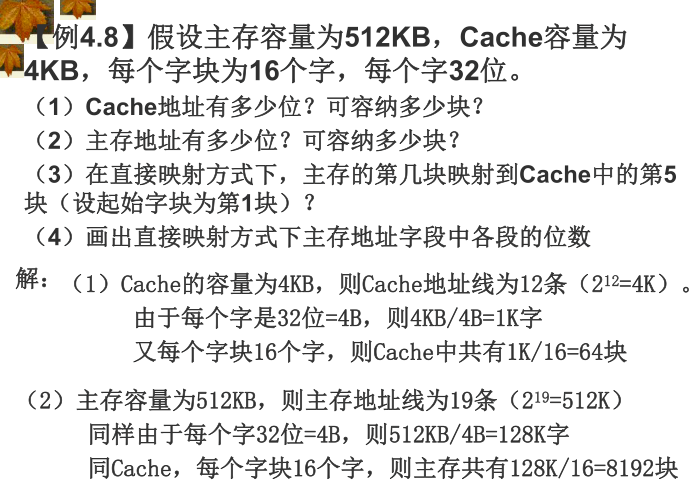

9.高速缓存(三种映射方法、主存地址划分、命中率、平均访问时间)

9.1知识储备

9.2典型例题

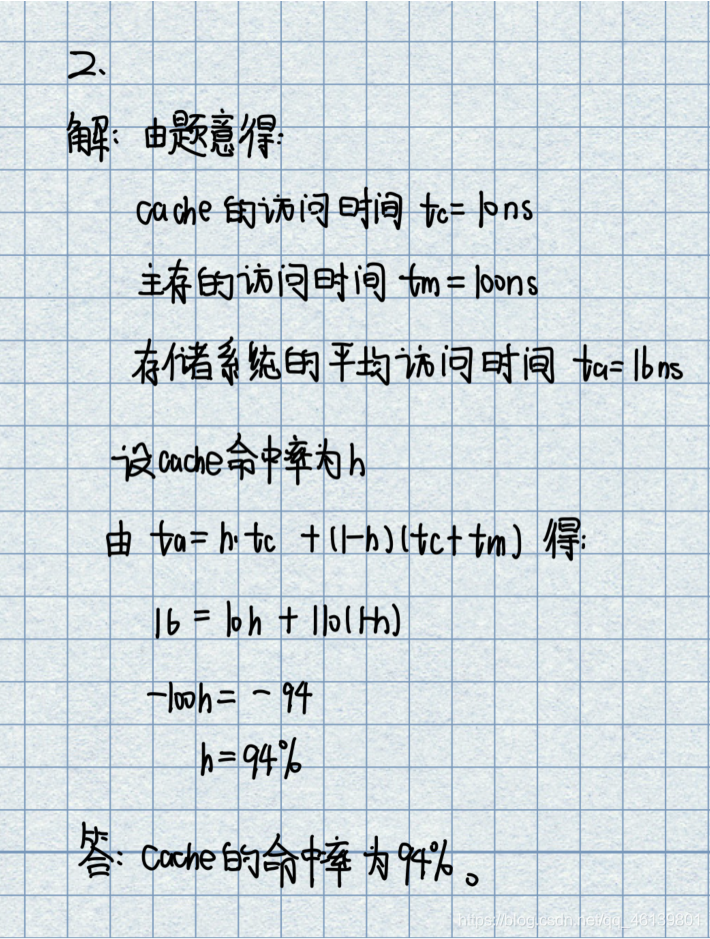

1.若cache以字为块,其存取时间为10ns,主存的存取时间为100ns,存储系统的平均存取时间为16ns, 则cache的命中率为()

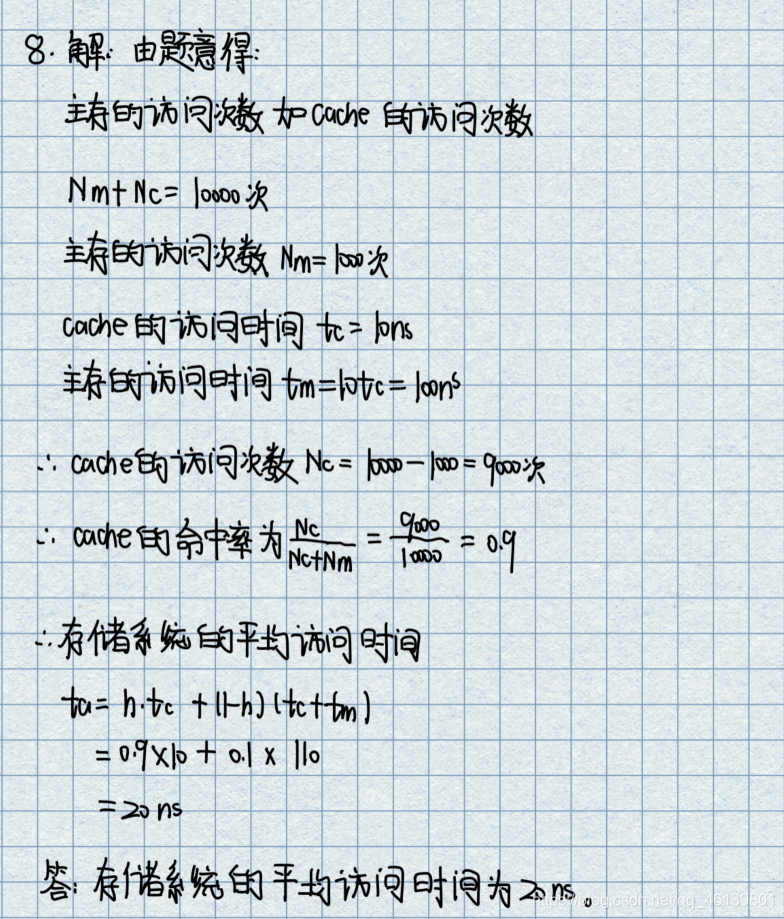

2.假设某计算机的存储系统由cache和主存组成,某程序执行过程中访存10000次 , 其中访问主存1000次,cache的访问时间是10ns,主存的访问时间是cache的10倍, 则存储系统的平均访问时间是?

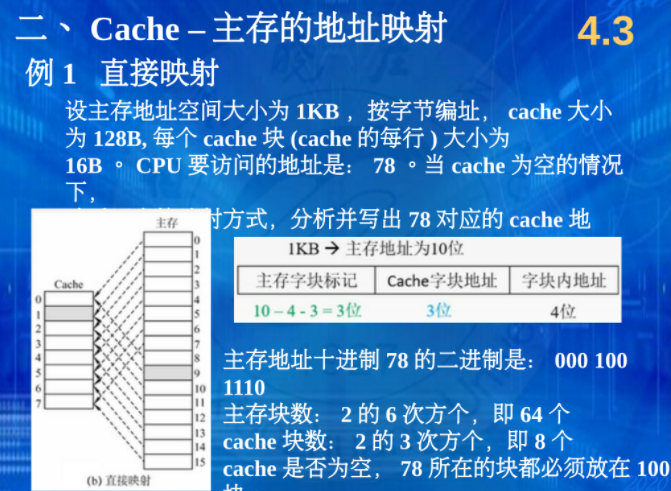

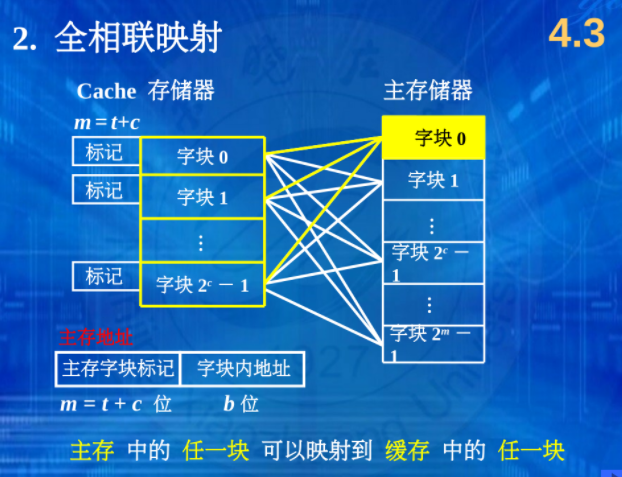

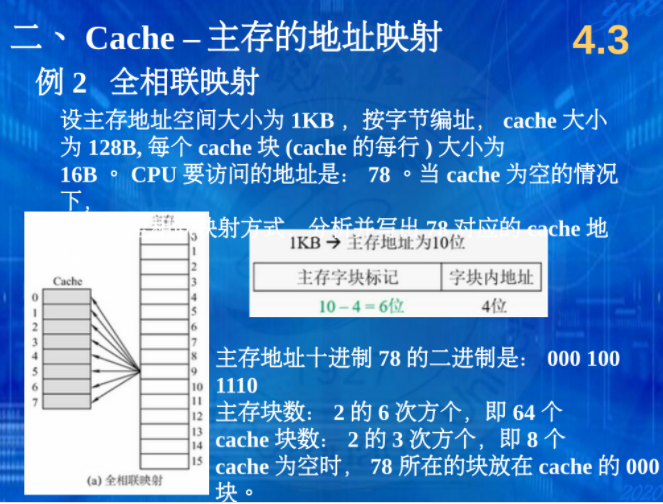

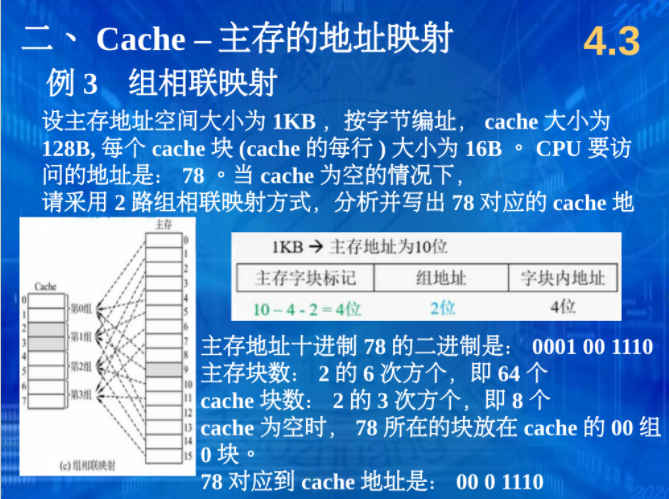

填空题:1、设主存地址空间大小为1KB,按字节编址,cache大小为128B,每个cache块(cache的每行)大小为16B。CPU要访问的地址是:196。当cache为空的情况下,主存地址是(1)位,主存地址十进制196的二进制是:(2),主存块数是:(3)个,cache块数是:(4)个,采用直接映射方式,不论cache是否为空,地址196所在的块(5)(必须或不一定)放在cache的(6)2块,196对应到cache地址是:(7)2。采用全相联映射时,196对应到cache地址是:(8)2;采用4路组相联映射时,196对应到cache地址是:(9)2。参考解答:(1)10(2)0011000100(3)64(4)8(5)必须(6)100(7)1000100(8)0000100(9)0000100解析:(1)主存地址空间大小为1KB—>主存地址为10位。(当cache为空时)(2)196=128+64+4,对应的二进制为0011000100(补全10位)(3)Cache—主存地址映射的实质:字块内地址一样,主存的块号—>Cache所在块块号,每个cache块(cache的每行)大小为16B—>字块内地址为4位,因此主存的地址为6位(10-4=6),主存的块数为2^6=64个。(4)cache大小为128B,每个cache块(cache的每行)大小为16B,cache的块数=128/16=8块。(5)直接映射方式:每个主存块只能和一个缓存块对应。因此填"必须"。(6)cache的块数为8块,则cache字块地址为3位(2^3=8)【取十进制196对应二进制的低5位到低7位,即(100)2;低4位为字块内地址,即(0100)2为字块内地址。】(7)cache地址包括cache字块地址(3位)和字块内地址(4位)【取十进制196对应二进制的低7位,即(1000100)2。】(8)全相联映射,主存中的任一块可以映射到缓存中的任一块,cache为空的情况下时,映射到cache中的第0块(即cache字块地址为(000)2的那一块),字块内地址不变。(9)cache共有8块,采用4路组相联映射时(组内cache块为4块),cache共分8/4=2组(2^1=2);因此主存地址中的组地址占1位,为十进制196对应二进制的从右往左数第5位0,所以cache中的组地址为0,又cache块为空,因此196对应到cache第0组的第00块中。2、某计算机的cache共有8块,假设为空,每个主存块大小为32字节(按字节编址),采用直接映像法,主存129号单元所在主存块应装入到的cache块号是(1);采用全相联映像法,主存129号单元所在主存块应装入到的cache块号是(2);采用4路组相联映像法,主存129号单元所在主存块应装入到的cache块号是(3)参考解答:每个主存块大小为32字节(按字节编址)故主存129号单元所在主存块为第129÷32=4块(块号从0开始编号)(1)直接映射方式下,主存块按模C(C为cache块数)映射到cache中的某一块,4 mod 8=4,故主存129号单元所在主存块应装入到的cache块号为4。(2)全相联映射方式下,主存块中的任一快可以映射到cache中的任一块。由于cache为空,故129号单元所在的主存块应装入块号为0的cache块中。(3)组相联映射方式下,主存块按模Q(Q为cache组数)映射到cache对应组中的任一块。cache共有8块,采用4路组相联映射(组内cache块为4块),故cache共分8÷4=2组,4 mod 2=0,由于cache为空,故129号单元所在主存块应装入cache第0组第0个cache块。3、某32位计算机的cache容量为16KB,cache行的大小为16B,若主存与cache地址映像采用直接映像方式,则主存地址为0x1234E8F8的单元装入cache的地址是()请给出解题过程参考解答:cache行大小为16B(2^4)—>字块内地址为4位cache块数=16*2^10B÷16B=2^10—>cache字块地址为10位十六进制主存地址0x1234E8F8的二进制为0001 0010 0011 0100 1110 1000 1111 1000取二进制低14位得装入cache的地址为10 1000 1111 1000

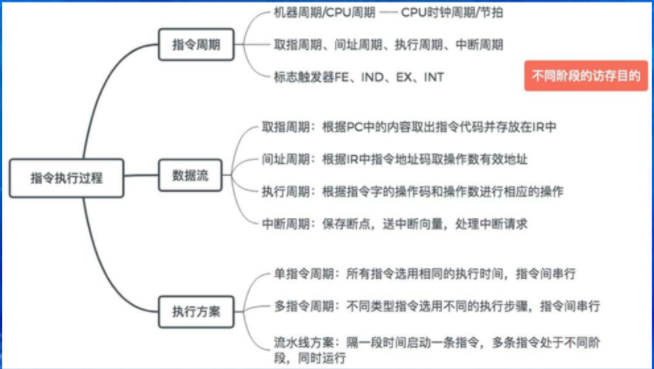

10.控制器(理解指令的四个周期对应微操作序列及所需对应的微命令)

10.1知识储备

10.2典型例题

1.请分析一般指令的执行过程,并给出每个阶段对应的微操作。

分析一条指令的执行过程

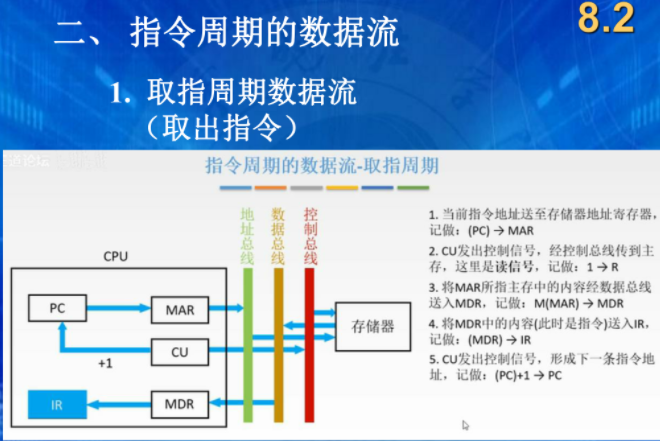

指令的执行过程可能有一个周期,只有取指周期;也可能有两个周期,取指周期和执行周期;

如果有间指操作的话,还包括了间指周期;如果有中断操作的话,还要执行中断周期。取指周期需要将指令从内存单元中取出,放入CPU的IR寄存器;

需要对指令的操作码部分进行分析(把操作码部分送给CU,由CU确定这是系统当中的哪一条指令); 需要对寻址方式进行分析。间指周期需要访问一次内存,把操作数的地址从内存单元取出。

执行周期包括完成指令要求的全部运算(从内存单元取出操作数、进行相应的运算操作并把运算结果保存在给定的寄存器当中)。如果有中断周期的话,在每条指令执行周期结束,要确认是否有中断请求。如果有中断请求,则需响应中断,

响应中断过程包括:保存断点、形成中断服务程序入口地址、硬件关中断。取值周期的微操作

要想把指令从内存单元当中取出,则需要知道指令的地址,而指令的地址保存在程序计数器(PC)中。

首先PC要把包含的指令地址送给MAR,再通过MAR把信号送给地址总线,最后送到存储器当中。

PC—>MAR—>地址总线—>存储器然后由控制单元向存储器发出读命令,读出的数据由数据总线送给MDR这个寄存器,

再由MDR送到IR当中,那么指令就被取到了IR寄存器。 1—>R M(MAR)—>MDR MDR—>IR取值周期可能还要完成译码的任务,译码来确定这条指令到底要做什么操作,所做的操作由指令的操作码部分给出。所以要把指令的操作码部分送给CU,CU去译码,来确认这条指令要做什么操作。

OP(IR)—>CU另外取值周期还要对PC进行拓展,指令取完,可以对PC中的内容进行更新,为取下一条指令做准备。

(PC)+1—>PC间指周期的微操作

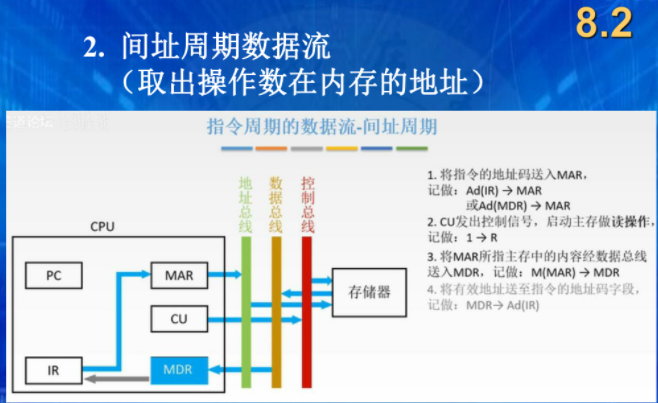

通过间指周期,把操作数的地址从存储器当中取出,放入到指令寄存器(IR)当中所保存的地址码部分。

首先将指令的形式地址(IR中的地址码部分)传送给MAR,再通过MAR传送到地址总线,进而传送到存储器的地址线上。要实现这个操作,控制器要发出将IR的地址码部分送给MAR的控制信号,然后由控制器向存储器发出读操作命令。存储器接收到地址和读操作命令以后,在指定的内存单元当中将操作数的地址取出,通过数据总线传输给MDR。

Ad(IR)—>MAR—>地址总线—>存储器 1—>R M(MAR)—>MDR被取出的地址进一步被送到IR寄存器的地址码部分,这个时候IR寄存器当中包含的指令的地址码部分就是操作数的物理地址(操作数所在的存储单元的地址)

MDR—>Ad(IR)执行周期的微操作

不同指令执行周期的微操作是不同的。

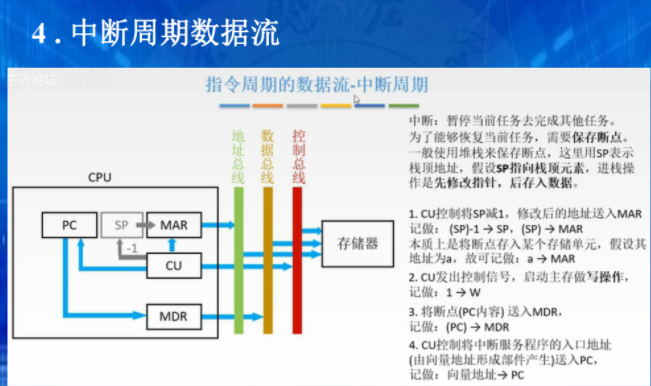

中断周期的微操作

中断周期三件事:保存断点、形成中断服务程序入口地址 、硬件关中断。

保存断点两种方法:1)程序断点保存入“0”地址2)程序断点进栈 1) 如果采用程序断点存入给定的一个地址,控制单元要把断点保存到内存中。 0—>MAR对存储器进行写操作,控制单元向存储器发出写命令。

1—>W程序断点进行保存,保存至程序计数器PC中,PC寄存器的内容保存入MDR。

PC—>MDR完成写入操作,将MDR的内容保存到MAR指定的内存单元中。

MDR—>M(MAR)形成中断服务程序入口地址,如果采用硬件向量法,把向量地址保存到PC中。

向量地址—>PC 形成中断服务程序入口地址,如果采用软件查询法,则需将中断识别程序的入口地址M—>PC,将来由CPU执行中断识别程序,来给出中断服务程序的入口地址。 M—>PC硬件关中断,将0送入到允许中断触发器中,实际的操作命令如下:

0— >EINT(置“0”)2)如果采用程序断点进栈,首先要修改栈顶,形成新的栈顶地址,将这个地址送给MAR。

(SP)-1—>MAR写操作,将PC的内容保存到内存单元中。

PC—>MDR完成写入操作,将MDR的内容保存到MAR指定的内存单元中。

MDR—>M(MAR)形成中断服务程序入口地址,如果采用硬件向量法,把向量地址保存到PC中。

向量地址—>PC形成中断服务程序入口地址,如果采用软件查询法,则需将中断识别程序的入口地址M—>PC,将来由CPU执行中断识别程序,来给出中断服务程序的入口地址。

M—>PC硬件关中断,将0送入到允许中断触发器中,实际的操作命令如下:

0—>EINT(置“0”)参考资料

转载地址:http://ltiki.baihongyu.com/